Die Prozessknoten von Intel werden von 20 A in diesem Jahr auf 14 A im Jahr 2027 steigen

Intel wird nächstes Jahr seinen 18A-Prozessknoten vorstellen

Aber ab der 20A-Produktion später in diesem Jahr wird Intel mit einer Schlüsselfunktion, die der amerikanische Chiphersteller PowerVia nennt (auch bekannt als Backside Power Delivery), einen kleinen Vorsprung gegenüber TSMC und Samsung Foundry haben. Es wird erwartet, dass TSMC diese Technologie mit seinem N2P-Knoten nutzt, den es ab 2026 nutzen wird. Samsung Foundry wird angeblich Backside Power Delivery auf einem bestimmten Knoten nutzen, der nächstes Jahr auf den Markt kommt, obwohl Samsung Foundry dies nicht bestätigt hat.

Was ist PowerVia? Die meisten kleinen Drähte, die einen Chip mit Strom versorgen, befinden sich auf allen Schichten, aus denen eine Siliziumkomponente besteht. Da diese Chips immer leistungsfähiger und komplexer werden, konkurrieren die Drähte oben, die mit den Stromquellen verbunden sind, mit den Drähten, die die Komponenten verbinden. Dies führt zu Energieverschwendung und geringer Effizienz.

PowerVia verlegt die Drähte, die die Chips mit Strom versorgen, auf die Rückseite des Chips. Dadurch können die Taktraten um 6 % erhöht werden, was zu einer höheren Leistung führt. Hinzu kommt die Leistungssteigerung durch die Verwendung eines fortschrittlicheren Prozessknotens, und das Ergebnis ist ein leistungsstärkerer Chip, der zum Betrieb eines leistungsstärkeren Geräts verwendet wird.

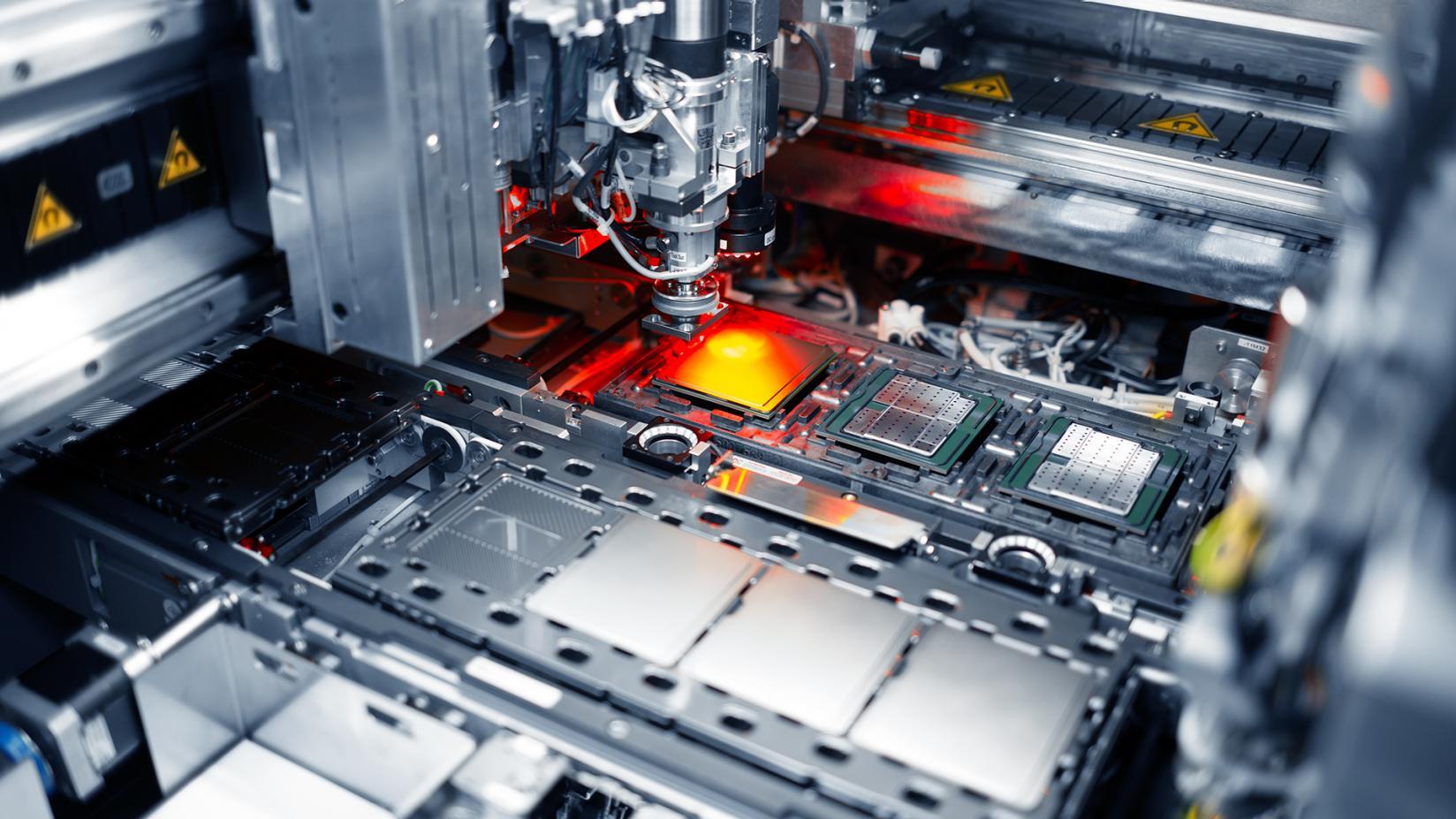

Intel ist das erste Unternehmen, das seine High-NA Extreme Ultraviolet Lithography-Maschine in Empfang nimmt

Gelsinger, CEO von Intel, sagte: „Ich habe das gesamte Unternehmen auf 18A gesetzt.“ Intel erwartet, dass die Leistung und Effizienz seines 18A-Knotens die Besten von TSMC übertreffen wird. Intel hat außerdem einen Vertrag mit Arm unterzeichnet, der es den Chipdesign-Kunden von Arm ermöglicht, SoCs mit geringem Stromverbrauch auf Basis des 18A-Prozessknotens von Intel zu bauen. Letzten Monat stimmte Intel zu, im 18A-Prozess einen maßgeschneiderten Chip für Microsoft zu bauen. Vier namentlich nicht genannte große Unternehmen (es ist nicht klar, ob Microsoft eines der vier ist) haben sich verpflichtet, Intel ihre Chips im 18A-Verfahren produzieren zu lassen.

Die älteren EUV-Geräte haben eine Apertur von 0,33 (entspricht einer Auflösung von 13 nm) und die High-NA-Geräte haben eine Apertur von 0,55 (entspricht einer Auflösung von 8 nm). Durch die Übertragung eines Musters mit höherer Auflösung auf einen Wafer könnte die Gießerei vermeiden, einen Wafer zweimal durch die EUV-Maschine laufen zu lassen, um zusätzliche Funktionen hinzuzufügen, was sowohl Zeit als auch Geld spart. Während TSMC und Samsung Foundry beide eine der High-NA-Maschinen bei ASML bestellt haben, wird Intel wahrscheinlich zuerst die zeitsparende Lithographiemaschine nutzen können.