Semiconductor engraving concerns many companies around the world, but only three are at the cutting edge of technology: Intel, Samsung and, the number one Taiwanese giant in the sector, TSMC.

The question of fineness of engraving did not interest many people twenty years ago. Today, however, figures expressed in nanometers are on many lips.

In the past, Intel experienced significant problems in moving to 10 nm and, it seems that it is now TSMC’s turn, “broken down” on 2 nm, or when the infinitely small plays tricks even on the largest businesses.

Nanosheet, nanoribbon and GAAFET in one boat

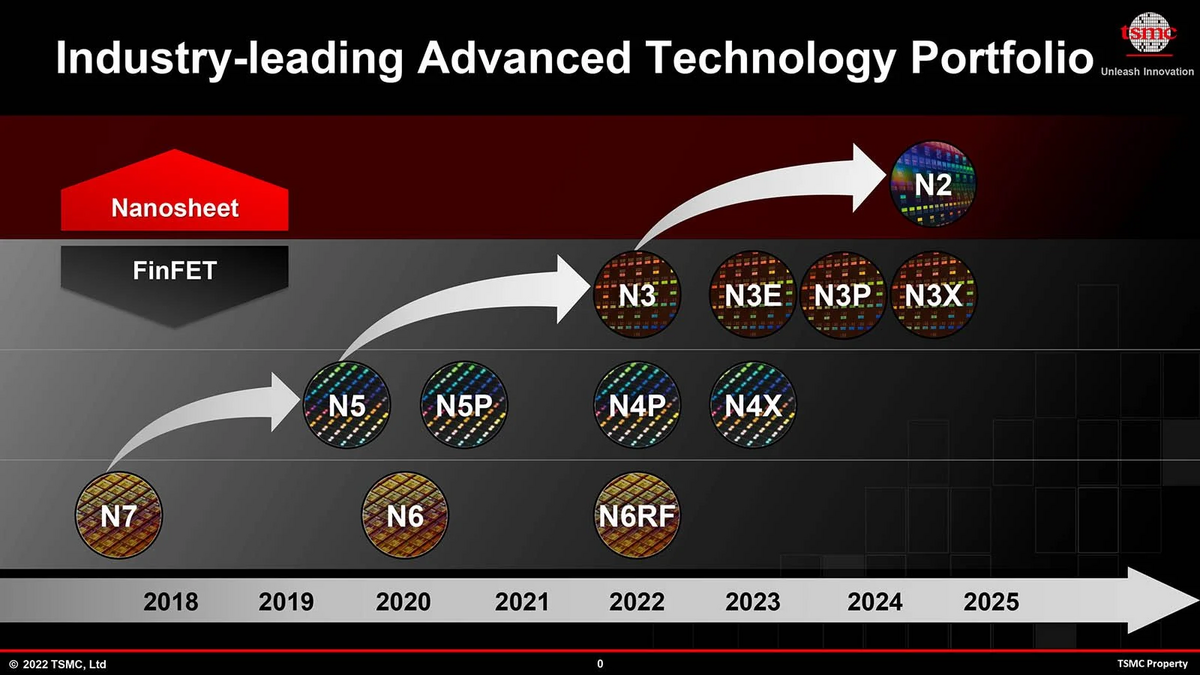

Rather discreet on the question of the 2nm engraving process, TSMC has nevertheless repeated several times that the deployment of this technology is planned for “during 2025”.

Internally and in official publications, this process is called N2 and should logically allow TSMC to gain a definite advantage over its two main competitors in this area, Samsung and Intel. Of course, such a process must also allow economies of scale – more chips on the same wafer – and improve the energy aspect.

For many years, TSMC relied for its etching processes on so-called FinFET or fin transistors, but this is no longer possible with such fine engraving. The N2 must therefore mark the transition to transistors “ nanosheet “, Or ” nanoribbon » at Intel and “ GAAFET » at Samsung.

Not fixing Apple’s affairs?

The problem perhaps comes from this change of transistors for TSMC. Let them be nanosheet “, ” nanoribbon ” Or ” GAAFET », They are all based on the need to better isolate the circuits, but are not simple to produce.

In reality, the concept of “ gate all around » (the GAA of GAAFET) is not new, but its manufacturing complexity forced manufacturers to instead focus on FinFET during the 2000s. Today, TechPowerUp tells us that TSMC could postpone the release of its N2 to 2026 and, of course, technical constraints resurface to explain this postponement.

Note that TSMC has not confirmed this information and that the rest is only hypothesis from our colleague who rightly points out that the transition to nanosheet transistors by the Taiwanese is only one of the many challenges that the Taiwanese must face the semiconductor giants. This is also the reason why there are only three companies still in the running.

In addition, the problem thus mentioned today would be different from the water supply difficulties which were discussed at the end of August to justify that TSMC was at a standstill on 2 nm chips.

If it were confirmed, this one-year postponement at TSMC would of course benefit Samsung, whose 3 nm is well underway, and Intel, which does not miss an opportunity to indicate that its Intel 4, Intel 20A and Intel 18A is progressing as planned. A delay at TSMC would not bode well for its main customers either, with Apple at the top of the list.

Source : TechPowerUp

1